# CALCOLATORI ELETTRONICI B – 19 marzo 2008

**NOME:**

**COGNOME:**

**MATR:**

Scrivere chiaramente in caratteri maiuscoli a stampa

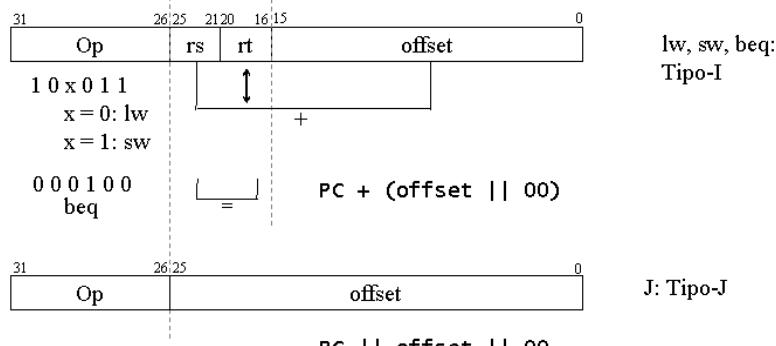

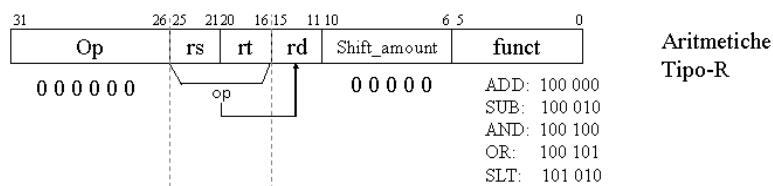

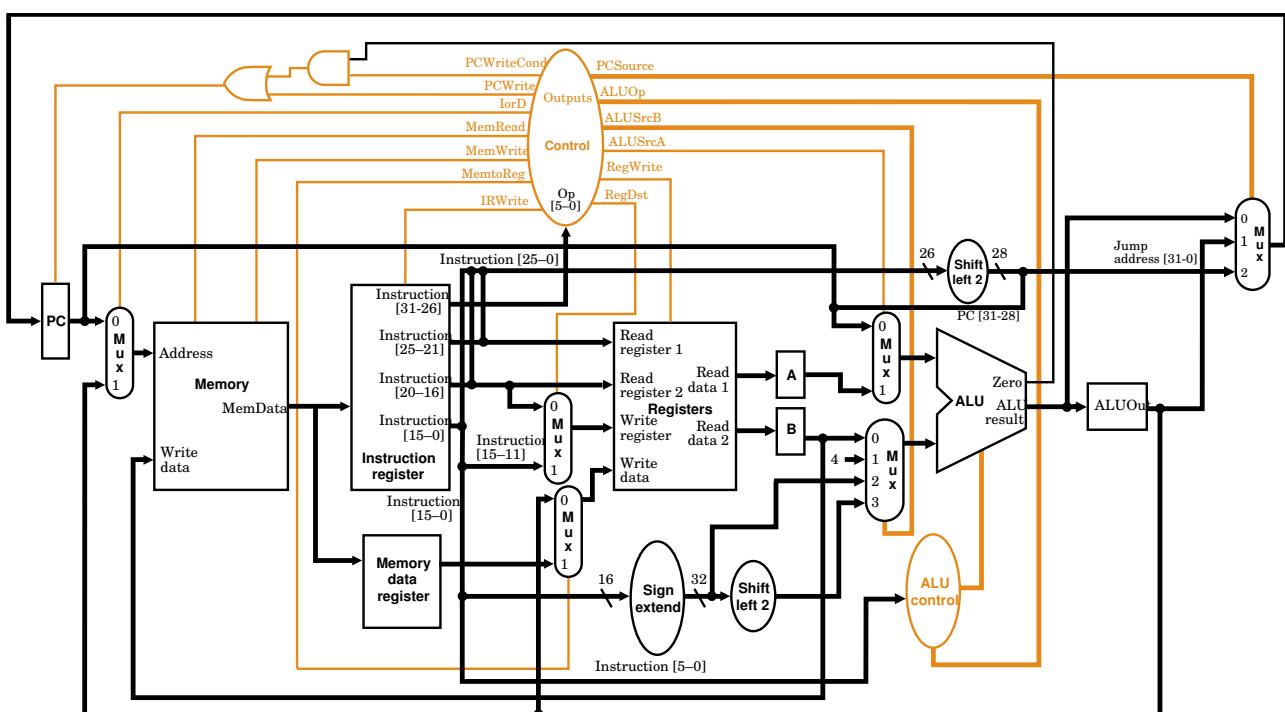

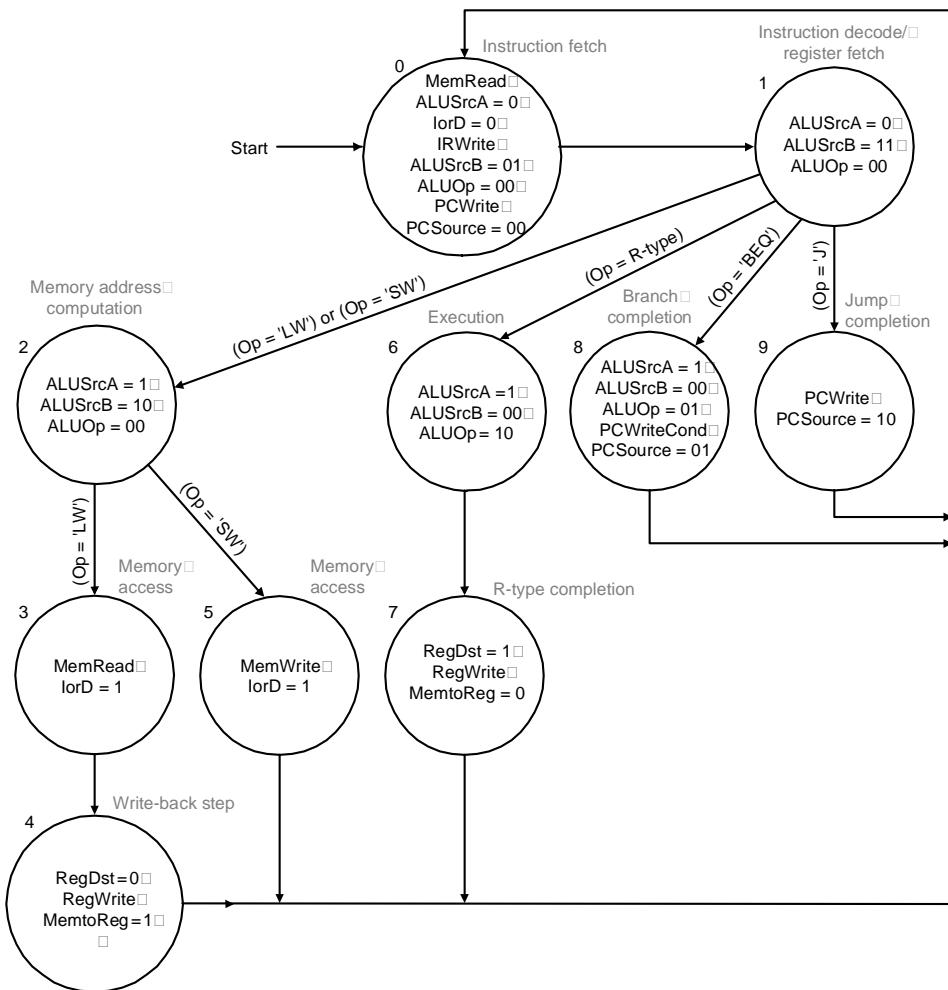

1. Si considerino, mostrati nelle figure alla pagina seguente, il datapath ed il diagramma a stati finiti che specifica l'unità di controllo secondo la tecnica a multiciclo relativamente alle istruzioni MIPS *lw*, *sw*, *beq*, *j* ed alle istruzioni *Tipo-R*.

Si vuole implementare la nuova istruzione

*lw rt, +(rs)* //  $rs \leftarrow rs + 4$ ,  $rt \leftarrow M[rs]$

che incrementa il registro *rs* in modo che punti alla parola successiva in memoria e carica nel registro *rt* il valore di tale locazione di memoria (di indirizzo specificato in *rs*).

Ricordando i tre formati di codifica delle istruzioni (riportati di seguito) si chiede di:

- riportare il formato della nuova istruzione macchina

- riportare, nella corrispondente figura, le modifiche necessarie al datapath

- estendere il diagramma degli stati per implementare la nuova istruzione

[6]

## Promemoria formati delle istruzioni:

2. Si consideri il seguente frammento di codice MIPS:

```

add    $t0, $t0, $s1

sub    $t1, $t0, $s1

lw     $t1, 20($t0)

sub    $s2, $t1, $t2

add    $s2, $t2, $t2

```

Si consideri l'implementazione con pipeline a 5 stadi (F: Fetch, D: Decode, E: Execute, M: Mem, W: Write-Back). Si chiede di:

- individuare in modo preciso tutte le dipendenze tra i dati

- tracciare il diagramma temporale delle istruzioni (indicando esplicitamente le eventuali propagazioni e, per ognuna di esse, quale dato è propagato) in ognuna delle seguenti ipotesi:

- non è disponibile alcuna unità di propagazione

- è disponibile un'unità di propagazione verso lo stadio E

- è disponibile un'unità di propagazione verso lo stadio E ed una verso lo stadio M.

Nei diagrammi, si chiede di indicare il numero di cicli di penalità.

[6]

3. Si consideri un processore MIPS implementato tramite la tecnica multiciclo (cfr. datapath e diagramma degli stati riportati nella figura dell'esercizio 1), in cui l'hardware richiede i seguenti tempi di esecuzione:

- prelievo istruzione e accesso alla memoria dati: 2 ns

- lettura e scrittura Register File: 1 ns

- operazione ALU: 2ns

- decodifica: 2 ns

Si assuma un carico di lavoro che prevede la seguente distribuzione delle istruzioni MIPS:

|         |      |

|---------|------|

| lw:     | 20 % |

| sw:     | 20 % |

| Tipo-R: | 40 % |

| beq:    | 15 % |

| j:      | 5 %  |

Si supponga inoltre che:

- il 30% delle istruzioni Tipo-R siano seguite da istruzioni che ne utilizzano il risultato;

- il 20% delle istruzioni lw siano seguite da istruzioni Tipo-R che ne utilizzano il risultato;

- il 10% delle istruzioni lw siano seguite da istruzioni sw che ne utilizzano il risultato per il calcolo dell'indirizzo;

- il 15 % delle istruzioni lw siano seguite da istruzioni sw che ne utilizzano il risultato per immagazzinarlo in memoria.

[NB: per semplicità, si trascuri il caso in cui una sw utilizza il risultato della lw sia per il calcolo dell'indirizzo sia per immagazzinarlo in memoria]

Si chiede di:

- calcolare il tempo medio di esecuzione

- calcolare il tempo medio di esecuzione supponendo che il tempo di decodifica si riduca a 1 ns

- calcolare il miglioramento delle prestazioni ottenuto utilizzando una pipeline dotata di unità di propagazione verso lo stadio E ed una verso lo stadio M (si considerino solo le criticità sui dati trascurando le criticità strutturali e le criticità sui salti).

Si giustifichino brevemente le risposte fornite.

[5]

4. Nell'ambito delle tecniche di controllo con pipeline, si consideri la tecnica del “salto ritardato” per la gestione delle criticità sui salti. Si assuma che vi sia un solo slot di ritardo. Motivando le risposte, si dica quali delle seguenti affermazioni sono esatte e quali sbagliate:

- L'hardware del processore esegue l'istruzione successiva ad un salto condizionato soltanto se questa è indipendente dalla condizione di salto, altrimenti la scarta.

- L'hardware del processore esegue comunque l'istruzione successiva al salto condizionato, sia nel caso in cui il salto viene eseguito sia nel caso in cui il salto non viene eseguito.

- Non vi è alcun accorgimento hardware per la gestione dei salti, la cui gestione è demandata interamente al programmatore (o al compilatore).

- Il programmatore (o il compilatore) deve fare in modo che il codice sia ordinato in modo tale da massimizzare le prestazioni, ma può comunque basarsi completamente sulla gestione dei salti da parte dell'hardware che garantisce la correttezza nell'esecuzione del codice.

- [3]

5. Si consideri una pipeline a 5 stadi in cui la valutazione della condizione di salto e l'aggiornamento del Program Counter avvengono nel terzo stadio (EX). Si valutino le due seguenti soluzioni progettuali per la gestione dei salti condizionati:

- Predizione statica di “salto non effettuato”

- Predizione dinamica che utilizza un BTB in grado di fornire un indirizzo di destinazione sempre corretto ed un’accuratezza nella predizione della condizione di salto pari all’80%

In particolare, detta  $P$  la percentuale con cui i salti condizionati in media effettuano il salto, si valuti quale delle due soluzioni è preferibile in funzione di  $P$ . [4]

6. Con riferimento alla tecnica di gestione della memoria virtuale mediante un TLB a 4 elementi e tabella delle pagine, si dica motivando brevemente la risposta quali delle seguenti situazioni [a, b, c] sono possibili, quali impossibili e perché: [3]

a)

TLB

| bit di validità | Numero di pagina virtuale | Numero di pagina fisica |

|-----------------|---------------------------|-------------------------|

| 1               | 000000000000000010        | 10000000                |

| 1               | 000000000000000010        | 11111111                |

| 0               | 000000000000001000        | 11000000                |

| 0               | 000000000000001111        | 11100000                |

b)

TLB

| bit di validità | Numero di pagina virtuale | Numero di pagina fisica |

|-----------------|---------------------------|-------------------------|

| 1               | 000000000000000010        | 10000000                |

| 0               | 000000000000000010        | 11111111                |

| 1               | 000000000000001000        | 11000000                |

| 1               | 000000000000001111        | 11100000                |

c)

TLB

| bit di validità | Numero di pagina virtuale | Numero di pagina fisica |

|-----------------|---------------------------|-------------------------|

| 1               | 000000000000000010        | 10000000                |

| 1               | 000000000000000011        | 11111111                |

| 0               | 000000000000001000        | 11000000                |

| 0               | 000000000000001111        | 11100000                |

Tabella delle pagine

bit di validità

|   |          |

|---|----------|

| 1 | 11111001 |

| 1 | 11111000 |

| 1 | 10000000 |

| 0 | 11111111 |

| 1 | 00000000 |

| 0 | .        |

| 0 | .        |

| . | .        |

| 0 | .        |

7. Indicare le principali differenze tra bus sincroni e bus asincroni. Individuare inoltre per ciascuna delle due tipologie di bus un contesto di applicazione adatto al suo utilizzo, indicandone le motivazioni. [4]